July 1990

DP8473 Floppy Disk Controller PLUS-2

National Semiconductor

This controller is a full featured floppy disk controller that is software compatible with the  $\mu$ PD765A, but also includes

many additional hardware and software enhancements.

These enhancements include additional logic specifically re-

quired for an IBM® PC, PC-XT®, PC-AT®, or PS/2® design.

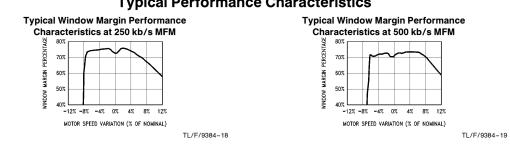

This controller incorporates a precision analog data separa-

tor, that includes a self trimming delay line and VCO. Up to

three external filters are switched automatically depending

on the data rate selected. This provides optimal perform-

ance at the standard PC data rates of 250/300 kb/s, and

500 kb/s. It also enables optimum performance at 1 Mb/s (MFM). These features combine to provide the lowest possi-

ble PLL bandwidth, with the greatest lock range, and hence

This controller includes write precompensation circuitry. A

shift register is used to provide a fixed 125 ns early-late

precompensation for all tracks at 500k/300k/250 kb/s (83 ns for 1 MB/s), or a precompensation value that scales with

# DP8473 Floppy Disk Controller PLUS-2<sup>™</sup>

# **General Description**

the widest window margin.

Features

- Fully µPD765A and IBM-BIOS compatible

- Integrates all PCXT<sup>®</sup>, PCAT<sup>®</sup>, and most PS/2<sup>®</sup> Logic On chip 24 MHz Crystal Oscillator

- DMA enable logic - IBM compatible address decode of A0-A2

- 12 mA µP bus interface buffers

- 48 mA floppy drive interface buffers

- Data rate and drive control registers Precision analog data separator

- Self-calibrating PLL and delay line

- Automatically chooses one of three filters

- Intelligent read algorithm

- Two pin programmable precompensation modes Other enhancements

- up to 1 Mb/s data rate

- Implied seek up to 4000 tracks

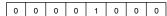

- IBM or ISO formatting

- Low power CMOS, with power down mode

(Continued)

© 1995 National Semiconductor Corporation TL/F/9384 RRD-B30M105/Printed in U. S. A.

# General Description (Continued)

the data rate, 83 ns/125 ns/208 ns/ 250 ns for data rates of 1.0M/500k/300k/250 kb/s respectively.

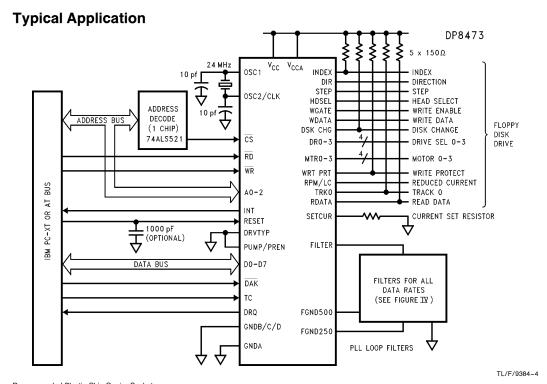

Specifically to support the PC-AT and PC-XT design, the Floppy Disk Controller PLUS-2 includes address decode for the A0–A2 address lines, the motor/drive select register, data rate register for selecting 250/300/500 kb/s, Disk Changed status, dual speed spindle motor control, low write current and DMA/interrupt sharing logic. The controller also supports direct connection to the  $\mu$ P bus via internal 12 mA buffers. The controller also can be connected directly to the disk drive via internal open drain high drive outputs, and Schmitt inputs.

In addition to this logic the DP8473 includes many features to ease design of higher performance drives and future controller upgrades. These include 1.0 Mb/s data rate, extended track range to 4096, Implied seeking, working Scan Commands, motor control timing, both standard IBM formats as well as Sony 3.5" (ISO) formats, and other enhancements.

# **Block Diagram**

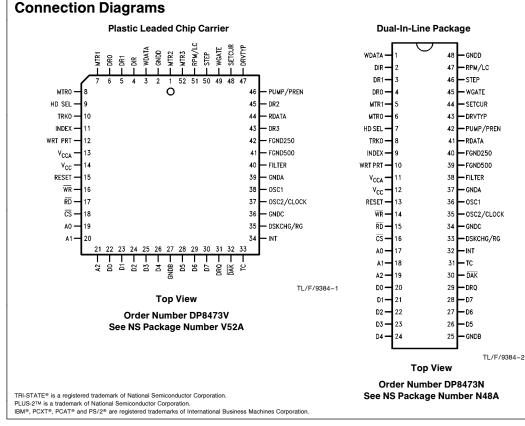

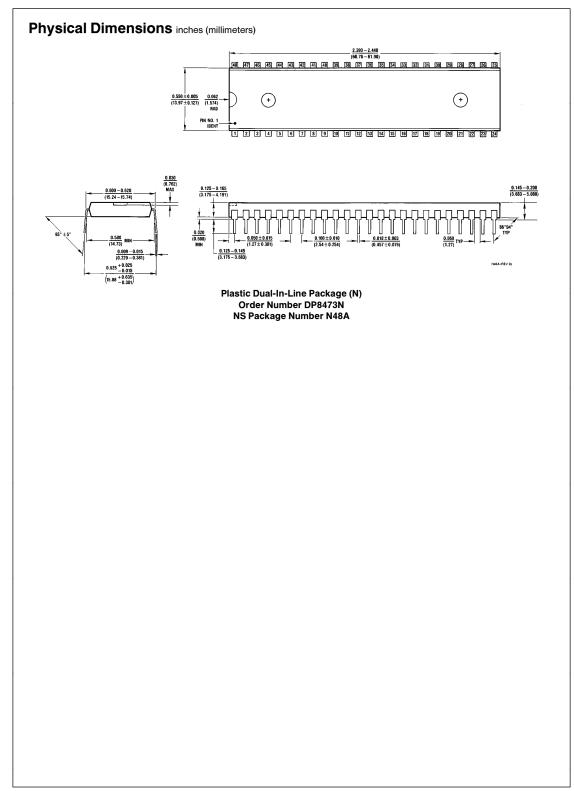

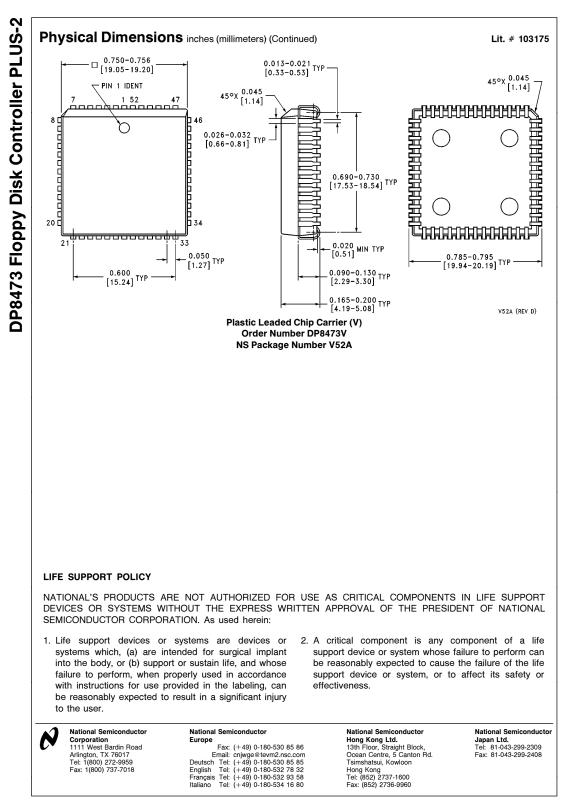

This device is available in a 52 pin Plastic Chip Carrier, and in a 48 pin Dual-In-Line package.

# **Table of Contents**

General Description Pin Description Functional Description Register Description Result Phase Register Description Processor Software Interface Command Description Table Command Descriptions DC and AC Characteristics

| Symbol     | DP8473<br>PCC | DP8473<br>DIP | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|---------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0, A1, A2 | 19–21         | 17–19         | Address lines from the microprocessor. This determines which registers the<br>microprocessor is accessing as shown in Table IV in the Register Description Section.<br>Don't care during DMA transfers.                                                                                                                                                                                                                                                                                           |

| CS         | 18            | 16            | Active low input to enable the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ inputs. Not required during DMA transfers. This should be held high during DMA transfers.                                                                                                                                                                                                                                                                                                                        |

| DAK        | 32            | 30            | Active low input to acknowledge the DMA request and enable the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ inputs. This signal is enabled when D3 of the Drive Control Register is set.                                                                                                                                                                                                                                                                                                     |

| DIR        | 4             | 2             | This output determines the direction of the head movement (low = step in, high = step out). When in the write or read modes, this output will be high. This is a high drive open drain output.                                                                                                                                                                                                                                                                                                    |

| DRQ        | 31            | 29            | Active high output to signal the DMA controller that a data transfer is needed. This signal<br>is enabled when D3 of the Drive Control Register is set.                                                                                                                                                                                                                                                                                                                                           |

| DRV TYP    | 47            | 43            | This is an input used by the controller to enable the 300 kb/s mode. This enables the use of floppy drives with either dual or single speed spindle motors. For dual speed spindle motors, this pin is tied low. When low, and 300 kb/s data rate is selected in the data rate register, the PLL actually uses 250 kb/s. This pin is tied high for single speed spindle motor drives (standard AT drive). When this pin is high and 300 kb/s is selected 300 kb/s is used. (See also RPM/LC pin). |

| DR0        | 6             | 4             | This is an active low drive select line for drive 0 that is controlled by the Drive Control register bits D0, D1. The Drive Select bit is ANDed with the Motor Enable of the same number. This is a high drive open drain output.                                                                                                                                                                                                                                                                 |

| DR1        | 5             | 3             | This is an active low drive select similar to DR0 line except for drive 1.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DR2        | 45            | _             | This is the same as DR0 except for drive 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DR3        | 43            | -             | This is the same as DR0 except for drive 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DSKCHG/RG  | 35            | 33            | This latched Schmitt input signal is inverted and routed to D7 of the data bus and is read when address xx7H is enabled. DSKCHG is a disk drive output that indicates when the drive door has been opened. When the RG bit in the Mode Command is set, this pin functions as a Read Gate signal that when low forces the data separator to lock to the crystal, and when high it locks to data for diagnostic purposes.                                                                           |

| D0-D4      | 22-26         | 20-24         | Bi-directional data lines to the microprocessor. These are the lower 5 bits and have buffered 12 mA outputs.                                                                                                                                                                                                                                                                                                                                                                                      |

| D5-D7      | 28–30         | 26–28         | Bi-directional data lines to the microprocessor. These upper 3 bits have buffered 12 mA outputs.                                                                                                                                                                                                                                                                                                                                                                                                  |

| FGND250    | 42            | 40            | This pin connects the PLL filter for 250k(MFM)/125k(FM) b/s or 300k(MFM)/150k(FM) b/s to ground. This is a low impedance open drain output.                                                                                                                                                                                                                                                                                                                                                       |

| FGND500    | 41            | 39            | This pin connects the PLL filter for 500k(MFM)/250k(FM) b/s to ground. This is a low impedance open drain output.                                                                                                                                                                                                                                                                                                                                                                                 |

| FILTER     | 40            | 38            | This pin is the output of the charge pump and the input to the VCO. One or more filters are attached between this pin and the GNDA, FGND250 and FGND500 pins.                                                                                                                                                                                                                                                                                                                                     |

| GNDA       | 39            | 37            | This pin is the analog ground for the data separator, including all primary and secondary PLLs and delay lines.                                                                                                                                                                                                                                                                                                                                                                                   |

| GNDB       | 27            | 25            | This pin is the digital ground for the 12 mA microprocessor interface buffers. This includes D0–D7, INT, and DRQ.                                                                                                                                                                                                                                                                                                                                                                                 |

| GNDC       | 36            | 34            | This pin is the digital ground for the controller's digital logic, including all internal register<br>micro-engine, etc.                                                                                                                                                                                                                                                                                                                                                                          |

| GNDD       | 2             | 48            | This pin is the digital ground for the disk interface output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HD SEL     | 9             | 7             | This output determines which disk drive head is active. Low = Head 1, Open (high) = Head 0. This is a high drive open drain output.                                                                                                                                                                                                                                                                                                                                                               |

| INDEX      | 11            | 9             | This active low Schmitt input signals the beginning of a track.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INT        | 34            | 32            | Active high output to signal that an operation requires the attention of the<br>microprocessor. The action required depends on the current function of the controller.<br>This signal is enabled when D3 of the Drive Control Register is set.                                                                                                                                                                                                                                                    |

| Symbol           | DP8473<br>PCC | DP8473<br>DIP | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTR0             | 8             | 6             | This is an active low motor enable line for drive 0, which is controlled by the Drive Contro register. This is a high drive open drain output.                                                                                                                                                                                                                                                                                                                                                         |

| MTR1             | 7             | 5             | This is an active low motor enable line for drive 1. Similar to MTR0.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MTR2             | 1             | _             | This is an active low motor enable line for drive 2. Similar to MTR0.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MTR3             | 52            |               | This is an active low motor enable line for drive 3. Similar to MTR0.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OSC1             | 38            | 36            | One side of an external 24 MHz crystal is attached here. This pin is tied low if an external clock is used.                                                                                                                                                                                                                                                                                                                                                                                            |

| OSC2/CLOCK       | 37            | 35            | One side of the external 24 MHz crystal is attached here. If a crystal is not used, a TTL or CMOS compatible clock is connected to this pin.                                                                                                                                                                                                                                                                                                                                                           |

| PUMP/PREN        | 46            | 42            | When the PU bit is set in Mode Command this pin is an output that indicates when the<br>charge pump is making a correction. Otherwise this pin is an input that sets the precomp<br>mode as shown in Table VI. If pin is configured as PUMP, PREN is assumed high.                                                                                                                                                                                                                                     |

| RD               | 17            | 15            | Active low input to signal a read from the controller to the microprocessor .                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RDATA            | 44            | 41            | The active low raw data read from the disk is connected here. This is a Schmitt input.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESET            | 15            | 13            | Active high input that resets the controller to the idle state, and resets all the output lines to the disk drive to their disabled state. The Drive Control register is reset to 00. The Data Rate register is set to 250 kb/s. The Specify command registers are not affected. The Mode Command registers are set to the default values. Reset should be held active during power up. To prevent glitches activating the reset sequence, a small capacitor (1000 pF) should be attached to this pin. |

| RPM/LC           | 51            | 47            | This high drive open drain output pin has two functions based on the selection of the DRVTYP pin.<br>1. When using a dual speed spindle motor floppy drive (DRVTYP pin low), this output is used to select the spindle motor speed, either 300 RPM or 360 RPM. In this mode this output goes low when 250/300 kb/data rate is chosen in the data rate register, and high when 500 kb/s is chosen.                                                                                                      |

|                  |               |               | <ol><li>When using a single speed spindle motor floppy drive (DRVTYP pin high), this pin<br/>indicates when to reduce the write current to the drive. This output is high for high density<br/>media (when 500 kb/s is chosen).</li></ol>                                                                                                                                                                                                                                                              |

| SETCUR           | 48            | 44            | An external resistor connected from this pin to analog ground programs the amount of<br>charge pump current that drives the external filters. The PLL Filter Design section shows<br>how to determine the values.                                                                                                                                                                                                                                                                                      |

| STEP             | 50            | 46            | This active low open drain high drive output will produce a pulse at a software programmable rate to move the head during a seek operation.                                                                                                                                                                                                                                                                                                                                                            |

| тс               | 33            | 31            | Active high input to indicate the termination of a DMA transfer. This signal is enabled when the DMA Acknowledge pin is active.                                                                                                                                                                                                                                                                                                                                                                        |

| TRK0             | 10            | 8             | This active low Schmitt input tells the controller that the head is at track zero of the selected disk drive.                                                                                                                                                                                                                                                                                                                                                                                          |

| WDATA            | 3             | 1             | This is the active low open drain write precompensated serial data to be written onto the selected disk drive. This is a high drive open drain output.                                                                                                                                                                                                                                                                                                                                                 |

| WGATE            | 49            | 45            | This active low open drain high drive output enables the write circuitry of the selected disk drive. This output has been designed to prevent glitches during power up and power down. This prevents writing to the disk when power is cycled.                                                                                                                                                                                                                                                         |

| WR               | 16            | 14            | Active low input to signal a write from the microprocessor to the controller.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WRT PRT          | 12            | 10            | This active low Schmitt input indicates that the disk is write protected. Any command that writes to that disk drive is inhibited when a disk is write protected.                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CC</sub>  | 14            | 12            | This pin is the 5V supply for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CCA</sub> | 13            | 11            | This pin is the 5V supply for the analog data separator circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Recommended Plastic Chip Carrier Socket: AMP P/N 821551-1 or equivalent.

#### FIGURE 2. DP8473 Typical Application

# **Functional Description**

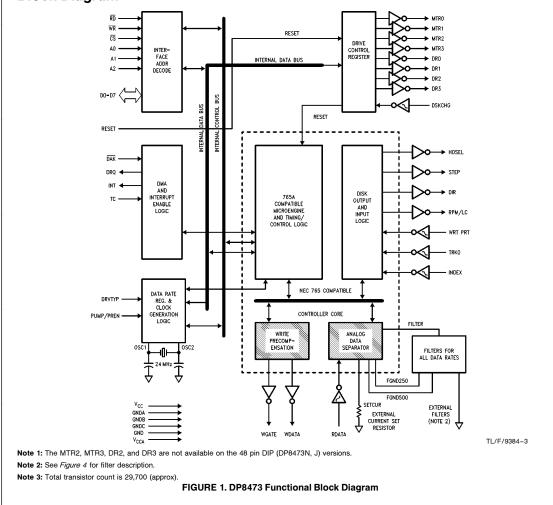

This section describes the basic architectural features of the DP8473, and many of the enhancements provided. Refer to *Figure 1.*

### 765A COMPATIBLE MICRO-ENGINE

The core of the DP8473 is a  $\mu$ PD765A compatible microcoded engine. This engine consists of a sequencer, program ROM, and disk/misc registers. This core is clocked by either a 4 MHz, 4.8 MHz or 8 MHz clock selected in the Data Rate Register. Upon this core is added all the glue logic used to implement a PC-XT or AT, or PS/2 floppy controller, as well as the data separator and write precompensation logic.

The controller consists of a microcoded engine that controls the entire operation of the chip including coordination of data transfer with the CPU, controlling the drive controls, and actually performing the algorithms associated with reading and writing data to/from the disk. This includes the read algorithm for the data separator.

Like the  $\mu$ PD765A, this controller takes commands and returns data and status through the Data Register in a byte serial fashion. Handshake for command/status I/O is provided via the Main Status Register. All of the  $\mu$ PD765A commands are supported, as are many other enhanced commands.

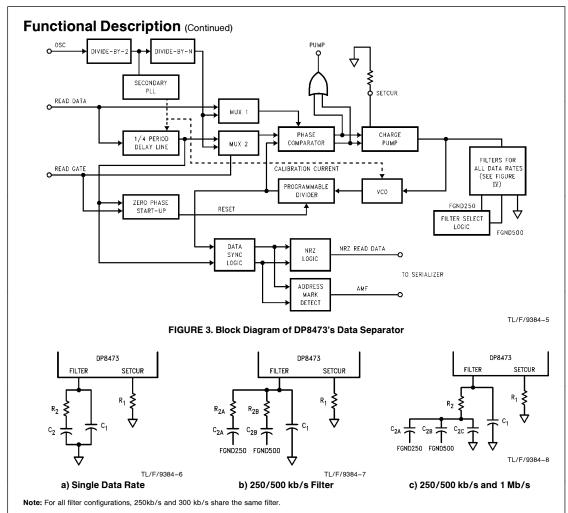

# DATA SEPARATOR

The internal data separator consists of an analog PLL and its associated circuitry. The PLL synchronizes the raw data signal read from the disk drive. The synchronized signal is used to separate the encoded clock and data pulses. The data pulses are de-serialized into bytes and then sent to the  $\mu P$  by the controller.

The main PLL consists of four main components, a phase comparator, a filter, a voltage controlled oscillator (VCO), and a programmable divider. The phase comparator detects the difference between the phase of the divider's output and the phase of the raw data being read from the disk. This phase difference is converted to a current which either charges or discharges one of the three external filters. The resulting voltage on the filter changes the frequency of the VCO and the divider output to reduce the phase difference between the input data and the divider's output. The PLL is "locked" when the frequency of the data read from the disk. A block diagram of the data separator is shown in *Figure 3*.

To ensure optimal performance, the data separator incorporates several additional circuits. The quarter period delay line is used to determine the center of each bit cell. A secondary PLL is used to automatically calibrate the quarter period delay line. The secondary PLL also calibrates the center frequency of the VCO.

To eliminate the logic associated with controlling multiple data rates the DP8473 supports the connection of three filters to the chip via the FGND250, and FGND500 pins (filter ground switches). The controller chooses which filter components to use based on the value loaded in the Data Rate Register. If 500 k(MFM) is being used then the FGND500 is enabled (FGND250 is disabled). If 250 k(MFM) or 300 k(MFM) is being used the FGND250 pin is enabled, and FGND500 is disabled. For 1 Mb/s (MFM) both FGND pins are disabled.

Note for FM encoding: Sometimes, after a reset, the DP8473 will consistently return an error in the Result Phase after an FM read command. If this occurs, simply reset the DP8473 and retry the operation. This may have to be done more than once, as many as five times. Resetting and repeating will prevent soft errors being reported prematurely. This technique is used by MS-DOS. Figure 4 shows several possible filter configurations. For a filter to cover all data rates (Figure 4c), the DP8473 has a 1 Mb/s filter always connected and other capacitor filter components for the other data rates are switched in parallel to this filter. The actual loop filter for 500 kb/s is the parallel combination of the two capacitors,  $C_{\text{2C}}$  and  $C_{\text{2B}},$  attached to the FGND500 pin and to ground. The 250/300 kb/s filter is the parallel combination of the capacitors, C<sub>2C</sub> and C<sub>2A</sub>, attached to the FGND250, and ground. If 1 Mb/s need not be supported then the filter configuration of Figure 4b can be used. This configuration allows more optimal performance for both 500k and 250/300 kb/s. Figure 4a is a simple filter configuration primarily for a single data rate (or multiple data rates with a performance compromise). Table II shows some typical filter values. Other filter configurations and values are possible, these result in good general performance. While the controller and data separator support both FM and MFM encoding, the filter switch circuitry only supports

# Functional Description (Continued)

the IBM standard MFM data rates. To provide both FM and MFM filters external logic may be necessary.

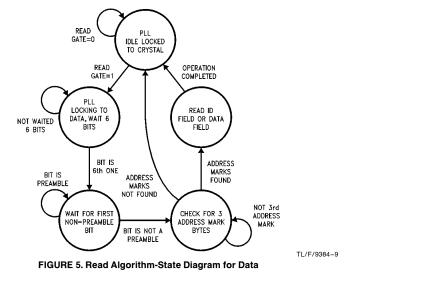

The controller takes best advantage of the internal data separator by implementing a sophisticated ID search algorithm. This algorithm, shown in *Figure 5*, enhances the PLL's lock characteristics by forcing the PLL to relock to the crystal any time the data separator attempts to lock to a non-preamble pattern. This algorithm ensures that the PLL is not thrown way out of lock by write splices or bad data fields.

# TABLE II. Typical Filter Values for the Various Data Rates (Assuming $\pm 6\%$ Capture Range)

| Data Rate                                 | C <sub>2</sub>                    | R <sub>2</sub> | C1         | R <sub>1</sub> |  |  |  |  |  |

|-------------------------------------------|-----------------------------------|----------------|------------|----------------|--|--|--|--|--|

| (MFM b/s)                                 | -2                                | 2              | •1         |                |  |  |  |  |  |

| Filter Values when Using All 3 Data Rates |                                   |                |            |                |  |  |  |  |  |

| 1.0M                                      | $C_{2C} = 0.012 \ \mu F$          | 560Ω           | 510 pF     | $5.6  k\Omega$ |  |  |  |  |  |

| 500k                                      | $C_{2B} = 0.015 \mu F$            |                |            |                |  |  |  |  |  |

| 250/300k                                  | $C_{2A} = 0.033 \ \mu F$          |                |            |                |  |  |  |  |  |

| Filter V                                  | alues when Using 2                | 250/300        | and 500 kl | o/s            |  |  |  |  |  |

| 500k                                      | $C_{2B} = 0.027 \ \mu F$          | 560Ω           | 1000 pF    | 5.6 kΩ         |  |  |  |  |  |

| 250/300k                                  | $C_{\text{2A}}=0.047~\mu\text{F}$ | $560\Omega$    |            |                |  |  |  |  |  |

|                                           | Filter Using Only One Data Rate   |                |            |                |  |  |  |  |  |

| 1.0M                                      | $C_2 = 0.012  \mu F$              | 560Ω           | 510 pF     | 5.6 kΩ         |  |  |  |  |  |

| 500k                                      | $C_2 = 0.027 \ \mu F$             | $560\Omega$    | 1000 pF    | $5.6  k\Omega$ |  |  |  |  |  |

| 300/250k                                  | $C_2=0.047~\mu\text{F}$           | $560\Omega$    | 2000 pF    | $5.6  k\Omega$ |  |  |  |  |  |

(These values are preliminary and thus are subject to change.)

#### TABLE III. Data Rates (MFM) versus VCO Divide-By Factor

| Tee Billiae By Factor |    |  |  |  |  |  |  |

|-----------------------|----|--|--|--|--|--|--|

| Data Rate             | N  |  |  |  |  |  |  |

| 1 Mb/s                | 4  |  |  |  |  |  |  |

| 500 kb/s              | 8  |  |  |  |  |  |  |

| 300 kb/s              | 16 |  |  |  |  |  |  |

| 250 kb/s              | 16 |  |  |  |  |  |  |

#### PLL DIAGNOSTIC MODES

In addition, the DP8473 has two diagnostic modes to enable filter optimization, 1) enabling the Charge Pump output signal onto the PUMP/PREN pin, and 2) providing external control of the Read Gate signal to the data separator. Both modes are enabled in the last byte of the Mode Command. The Pump output signal indicates when the charge pump is making a phase correction, and hence whether the loop is locked or not.

The Read Gate function, when enabled, allows the designer to manually force the data separator to lock to the incoming data or back to the reference clock. This enables easy verification of the lock characteristics of the PLL, by monitoring the FILTER pin, and the Pump signal.

# PLL FILTER DESIGN

This section provides information to enable design of the data separator's external filter and charge pump set resistor. This discussion is for a single data rate filter, and can be easily extrapolated to the other filters of *Figure 4*. Table II shows some typical filter component values, but if a custom filter is desired, the following parameters must be considered:

R<sub>1</sub>: Charge pump current setting resistor. The current set by this resistor is multiplied by the charge pump gain, K<sub>P</sub> which is ~2.5. Thus the charge pump current is:

$I_{PUMP}=$  (2.5) 1.2V/R<sub>1</sub>. R<sub>1</sub> should be set to between 3-12 k $\Omega.$  This resistor determines the gain of the phase detector, which is K<sub>D</sub> =  $I_{PUMP}/2\pi.$

# Functional Description (Continued)

- $\label{eq:C2} C_2: \qquad \mbox{Filter capacitor in series with $R_2$. With pump current this determines loop bandwidth.}$

- R<sub>2</sub>: Filter resistor. Determines the PLL damping factor.

- C<sub>1</sub>: This filter capacitor improves the performance of the PLL by providing additional filtering of bit jitter and noise.

- $K_{VCO}$ : The ratio of the change in the frequency of the VCO output due to a voltage change at the VCO input.  $K_{VCO}\approx 25~Mrad/s/V.$  The VCO is followed by a divider to achieve the desired frequency for each data rate. VCO center frequency is 4 MHz for data rates of 1 Mb/s, 500 kb/s, and 250 kb/s (MFM), and is 4.8 MHz for 300 kb/s (MFM).

- $K_{PLL}:$  This is the gain of the internal PLL circuitry, and is the product of  $V_{REF} \times K_{VCO} \times K_P$ . This value is specified in the Phase Locked Loop Characteristics table.

- $\omega_n$ : This is the bandwidth of the PLL, and is given by,

$$\omega_{\rm n} = \sqrt{\frac{{\rm K}_{\rm PLL}}{2\pi {\rm C}_2 {\rm N} \, {\rm R}_1}}$$

where N is the number of VCO cycles between two phase comparisons. The value of N for the various data rates are shown in Table III.

ζ: The damping factor is set to 0.7 to 1.2 and is given by,

$$\zeta = \frac{\omega_{n}R_{2}C_{2}}{2}$$

The trade off, when choosing filter components is between acquisition time while the PLL is locking and jitter immunity while reading data. To select the proper components for a standard floppy disk application the following procedure can be used:

1. Choose FM or MFM, and data rate. Determine N from Table III. Determine preamble length (MFM = 12). The PLL should lock within  $\frac{1}{2}$  the preamble time.

2. Determine loop bandwidth ( $\omega_n$ ) required, and set the charge pump resistor R<sub>1</sub>.

3. Calculate C<sub>2</sub> using:

$$C_2 = \frac{K_{PLL}}{2\pi R_1 N \omega_n^2}$$

4. Choose R<sub>2</sub> using:

$R_2 = \frac{2\zeta}{\omega_n C_2}$  6. Select  $C_1$  to be about  $1/_{20}$  th of  $C_2$ .

The above procedure will yield adequate loop performance. If optimum loop performance is required, or if the nature of the loop performance is very critical, then some additional consideration must be given to choosing  $\omega_n$  and the damping factor. (For a detailed description on how to choose  $\omega_n$  and  $\zeta$ , see: **AN-505 Floppy Disk Data Separator Design Guide for the DP8473**).

#### WRITE PRECOMPENSATION

The DP8473 incorporates a single fixed 3-bit shift register. This shift register outputs are tapped and multiplexed onto the write data output. The taps are selected by a standard precompensation algorithm. This precompensation value can be selected from the PUMP/PREN pin. When this pin is low 125 ns precomp is used for all data rates except 1 Mb/s which uses 83 ns. When PREN is tied high, the precompensation-value scales with data rate at 250 kb/s its 250 ns, for 300 kb/s its 208 ns, at 500 kb/s its 125 ns, and at 1.0 Mb/s its 83 ns. These values are shown in Table VI.

#### PC-AT AND PC-XT LOGIC BLOCKS

This section describes the major functional blocks of the PC logic that have been integrated on the controller. Refer back to *Figure 1*, the block diagram.

**DMA Enable Logic:** This is gating logic that disables the DMA lines and the Interrupt output, under the control of the DMA Enable bit in the Drive control register. When the DMA Enable bit is 0 then the INT, and DRQ are held TRI-STATE, and DAK is disabled.

**Drive Output Buffers/Input Receivers:** The drive interface output pins can drive  $150\Omega \pm 10\%$  termination resistors. This enables connection to a standard floppy drive. All drive interface inputs are TTL compatible schmitt trigger inputs with typically 250 mV of hysteresis. *The only functional differences between the 52 pin PLCC and the 48 pin DIP version are that the MTR2 and 3, and DR2 and 3 pins have been removed in order to accommodate the 48 pin package.*

**Bus Interface-Address Decode:** The address decode circuit allows software access to the controller, Drive Control Register, and Data Rate Register (see Table IV for the memory map) using the same address map as is used in the XT, AT, or PS/2. The decoding is provided for A0–A2, so only a single address decoder connected to the chip select is needed to complete the decode. The bus interface logic includes the 8-bit data bus and DRQ/INT signals. The output drive for these pins is 12 mA.

# TABLE IV. Address Memory Map for DP8473

| A2 | A1 | <b>A</b> 0 | R/W | Register               |  |  |

|----|----|------------|-----|------------------------|--|--|

| 0  | 0  | 0          | х   | None (Bus TRI-STATE)   |  |  |

| 0  | 0  | 1          | х   | None (Bus TRI-STATE)   |  |  |

| 0  | 1  | 0          | w   | Drive Control Register |  |  |

| 0  | 1  | 1          | Х   | None (Bus TRI-STATE)   |  |  |

| 1  | 0  | 0          | R   | Main Status Register   |  |  |

| 1  | 0  | 1          | R/W | Data Register          |  |  |

| 1  | 1  | 0          | Х   | None (Bus TRI-STATE)   |  |  |

| 1  | 1  | 1          | W   | Data Rate Register     |  |  |

| 1  | 1  | 1          | R   | Disk Changed Bit*      |  |  |

\*When this location is accessed only bit D7 is driving, all others are held TRI-STATE.

**Drive Control Register:** This 8-bit write only register controls the drive selects, motor enables, DMA enable, and Reset. See Register Description.

**Reset Logic:** The reset input pin is active high, and directly feeds the Drive Control Register and the Data Rate Register. After a hardware reset the Drive Control Register is reset to all zeros, and the Data Rate Register is set to 250 kb/s data rate. The controller is held reset until the software sets the Drive Control reset bit, after which the controller may be initialized. A software reset to the controller core can be issued by resetting then setting this bit. A software reset does not reset the Drive Control Register, or the Data Rate Register.

# Functional Description (Continued)

Data Rate Register and Clock Logic: This is a two bit register that controls the data rate that the controller uses. See Register Description. This register feeds logic that selects the data rates by programming a prescaler that divides the crystal or clock input by either 3, 5, or 6. This causes either 4 MHz, 4.8 MHz and 8 MHz to be input as the master clock for the controller core. If the Drive Type pin is high and a 300 kb/s data rate is chosen, 4.8 MHz is used to generate 300 kb/s, but when the DRVTYP pin is low and 300 kb/s is selected, 4 MHz is used, and the actual data rate is 250 kb/s. See Table VI.

Low Power Mode Logic: This logic is an enhancement over the standard XT, AT, PS/2 design. In the Low Power Mode the crystal oscillator, controller and all linear circuitry are turned off. When the oscillator is turned off the controller will typically draw about 1 mA. The internal circuitry is disabled while the oscillator is off because the internal circuitry is driven from this clock. The oscillator will turn back on automatically after it detects a read or a write to the Main Status or Data Registers. It may take a few milli-seconds for the oscillator to stabilize and the  $\mu P$  will be prevented from trying to access the Data Register during this time through the normal Main Status Register protocol. (The Request for Master bit in the Main Status Register will be inactive.) There are two ways to go into the low power mode. One is to command the controller to switch to low power immediately. The other method is to set the controller to automatically go into the low power mode 500 ms after the beginning of the idle state (based on a 500 kb/s (MFM) data rate). This would be invisible to the software. The low power mode is programmed through the Mode Command.

The Data Rate Register and the Drive Control Register are unaffected by the power down mode. They will remain active. It is up to the user to ensure that the Motor and Drive select signal are turned off.

#### **TABLE V. Truth Table for Drive Control Register**

| D7 | D6 | D5 | D4 | D1 | D0 | Function                      |

|----|----|----|----|----|----|-------------------------------|

| х  | Х  | Х  | 1  | 0  | 0  | Drive 0 Selected (DR0 = 0)    |

| X  | Х  | 1  | Х  | 0  | 1  | Drive 1 Selected (DR1 = $0$ ) |

| X  | 1  | Х  | Х  | 1  | 0  | Drive 2 Selected (DR2 = $0$ ) |

| 1  | х  | х  | Х  | 1  | 1  | Drive 3 Selected (DR3 = $0$ ) |

**Crystal Oscillator:** The DP8473 is clocked by a single 24 MHz signal. An on-chip oscillator is provided, to enable the attachment of a crystal, or a clock. If a crystal is used, a 24 MHz fundamental mode, parallel resonant crystal should be used. This crystal should be specified to have less than 40 $\Omega$  series resistance, and shunt capacitance of less than 7 pF. Low profile and surface mount crystals should be avoided due to their high start-up resistance, which could prohibit the circuit from oscillating.

If an external oscillator circuit is used, it must have a duty cycle of at least 40–60%, and minimum input levels of 2.4V and 0.4V. The controller should be configured so that the clock is input into the OSC2 pin, and OSC1 is tied to ground.

Crystals: NEL Frequency Controls: NEL-54024-2 NEL-C2800N SaRonix: SRX 3164

# Register Description

This section describes the register bits for all the registers that are directly accessible to the  $\mu$ P. Table IV (previous page) shows the memory map for these registers. Note that in the PC some of the registers are partially decoded, this is not the case here. All registers occupy only their documented addresses.

### MAIN STATUS REGISTER (Read Only)

The read only Main Status Register indicates the current status of the disk controller. The Main Status Register is always available to be read. One of its functions is to control the flow of data to and from the Data Register. The Main Status Register indicates when the disk controller is ready to send or receive data. It should be read before each byte is transferred to or from the Data Register except during a DMA transfer. No delay is required when reading this register after a data transfer.

D7 Request for Master: Indicates that the Data Register is ready to send or receive data from the  $\mu$ P. This bit is cleared immediately after a byte transfer and will become set again as soon as the disk controller is ready for the next byte.

**D6 Data Direction:** Indicates whether the controller is expecting a byte to be written to (0) or read from (1) the Data Register.

**D5 Non-DMA Execution:** Bit is set only during the Execution Phase of a command if it is in the non-DMA mode. In other words, if this bit is set, the multiple byte data transfer (in the Execution Phase) must be monitored by the  $\mu$ P either through interrupts, or software polling as described in the Processor Software Interface section.

**D4 Command in Progress:** Bit is set after the first byte of the Command Phase is written. Bit is cleared after the last byte of the Result Phase is read. If there is no result phase in a command, the bit is cleared after the last byte of the Command Phase is written.

**D3 Drive 3 Seeking:** Set after the last byte of the Command Phase of a Seek or Recalibrate command is issued for drive 3. Cleared after reading the first byte in the Result Phase of the Sense Interrupt Command for this drive.

D2 Drive 2 Seeking: Same as above for drive 2.

D1 Drive 1 Seeking: Same as above for drive 1.

D0 Drive 0 Seeking: Same as above for drive 0.

# DATA REGISTER (Read/Write)

This is the location through which all commands, data and status flow between the CPU and the DP8473. During the Command Phase the  $\mu$ P loads the controller's commands into this register based on the Status Register Request for Master and Data Direction bits. The Result Phase transfers the Status Registers and header information to the  $\mu$ P in the same fashion.

# **Register Description** (Continued)

TABLE VI. Data Rate and Precompensation Programming Values

| ······································ |      |               |                            |                            |                               |                        |                        |  |  |  |

|----------------------------------------|------|---------------|----------------------------|----------------------------|-------------------------------|------------------------|------------------------|--|--|--|

| D1                                     | D0** | DRVTYP<br>Pin | Data Rate<br>MFM<br>(kb/s) | Normal<br>Precomp*<br>(ns) | Alternate<br>Precomp*<br>(ns) | FGND<br>Pin<br>Enabled | RPM/LC<br>Pin<br>Level |  |  |  |

| 0                                      | 0    | х             | 500                        | 125                        | 125                           | FGND500                | High                   |  |  |  |

| 0                                      | 1    | 0             | 250                        | 125                        | 250                           | FGND250                | Low                    |  |  |  |

| 0                                      | 1    | 1             | 300                        | 208                        | 208                           | FGND250                | Low                    |  |  |  |

| 1                                      | 0    | 0             | 250                        | 125                        | 250                           | FGND250                | Low                    |  |  |  |

| 1                                      | 0    | 1             | 250                        | 125                        | 250                           | FGND250                | Low                    |  |  |  |

| 1                                      | 1    | 0             | 1000                       | 83                         | 83                            | None                   | High                   |  |  |  |

| 1                                      | 1    | 1             | 1000                       | 83                         | 83                            | None                   | Low                    |  |  |  |

\*Normal values when PUMP/PREN pin set low; Alternate values when PUMP/PREN pin set high.

\*\*D0 and D1 are Data Rate Control Bits.

# **DRIVE CONTROL REGISTER (Write Only)**

**D7 Motor Enable 3:** This controls the Motor for drive 3, MTR3. When 0 the output is high, when 1 the output is low. (Note this signal is not output to a pin on 48 pin DIP version.)

**D6 Motor Enable 2:** Same function as D7 except for drive 2's motor. (Note this signal is not brought out to a pin on DIP.)

**D5 Motor Enable 1:** This bit controls the Motor for drive 1's motor. When this bit is 0 the MTR1 output is high.

**D4 Motor Enable 0:** Same as D5 except for drive 0's motor. **D3 DMA Enable:** When set to a 1 this enables the DRQ, DAK, INT pins. A zero disables these signals.

**D2 Reset Controller:** This bit when set to a 0 resets the controller, and when a 1 enables normal operation. It does not affect the Drive Control or Data Rate Registers which are reset only by a hardware reset.

**D1-D0 Drive Select:** These two pins are encoded for the four drive selects, and are gated with the motor enable lines, so that only one drive is selected when it's Motor Enable is active. (See Table V.)

### DATA RATE REGISTER (Write Only)

#### D7-D2: Not used.

**D1, D0 Data Rate Select:** These bits set the data rate and the write precompensation values for the disk controller. After a hardware reset these bits are set to 10 (250 kb/s). They are encoded as shown in Table VI.

# DISK CHANGED REGISTER (Read Only)

**D7 Disk Changed:** This bit is the latched complement of the Disk Changed input pin. If the DSKCHG input is low this bit is high.

**D6-D0:** These bits are reserved for use by the hard disk controller, thus during a read of this register, these bits are TRI-STATE.

# **Result Phase Status Registers**

The Result Phase of a command contains bytes that hold status information. The format of these bytes are described below. Do not confuse these register bytes with the Main Status Register which is a read only register that is always available. The Result Phase status registers are read from the Data Register only during the Result Phase.

# STATUS REGISTER 0 (ST0)

# D7–D6 Interrupt Code:

00 = Normal Termination of Command.

01 = Abnormal Termination of Command. Execution of Command was started, but was not successfully completed.

10 = Invalid Command Issue. Command Issued was not recognized as a valid command.

11 = Ready changed state during the polling mode.

# **Result Phase Status Registers** (Continued)

- **D5 Seek End:** Seek or Recalibrate Command completed by the Controller. (Used during Sense Interrupt command.)

- D4 Equipment Check: After a Recalibrate Command, Track 0 signal failed to occur. (Used during Sense Interrupt command.)

- D3 Not Used: 0

- D2 Head Address (at end of Execution Phase).

- D1, D0 Drive Select (at end of Execution Phase).

- 00 = Drive 0 selected. 01 = Drive 1 selected.

- 10 = Drive 2 selected. 11 = Drive 3 selected.

#### **STATUS REGISTER 1 (ST1)**

**D7 End of Track:** Controller transferred the last byte of the last sector without the TC pin becoming active. The last sector is the End Of Track sector number programmed in the Command Phase.

#### D6 Not Used: 0

- D5 CRC Error: If this bit is set and bit 5 of ST2 is clear, then there was a CRC error in the Address Field of the correct sector. If bit 5 of ST2 is set, then there was a CRC error in the Data Field.

- D4 Over Run: Controller was not serviced by the  $\mu$ P soon enough during a data transfer in the Execution Phase.

#### TABLE VII. Maximum Time Allowed to Service an Interrupt or Acknowledge a DMA Request in Execution Phase

| Data<br>Rate | Time to<br>Service |  |  |  |

|--------------|--------------------|--|--|--|

| 125          | 62.0 μs            |  |  |  |

| 250          | 30.0 µs            |  |  |  |

| 500          | 14.0 μs            |  |  |  |

| 1000         | 6.0 μs             |  |  |  |

Time from rising edge of DRQ or INT to trailing edge of DAK or RD or WR. D3 Not Used: 0

- **D2** No Data: Three possible problems: 1) Controller cannot find the sector specified in the Command Phase during the execution of a Read, Write, or Scan command. An address mark was found however so it is not a blank disk. 2) Controller cannot read any Address Fields without a CRC error during Read ID command. 3) Controller cannot find starting sector during execution of Read A Track command.

- **D1 Not Writable:** Write Protect pin is active when a Write or Format command is issued.

D0 Missing Address Mark: If bit 0 of ST2 is clear then the disk controller cannot detect any Address Field Address Mark after two disk revolutions. If bit 0 of ST2 is set then the disk controller cannot detect the Data Field Address Mark.

# STATUS REGISTER 2 (ST2)

# D7 Not Used: 0

- D6 Control Mark: Controller tried to read a sector which contained a deleted data address mark during execution of Read Data or Scan commands. Or, if a Read Deleted Data command was executed, a regular address mark was detected.

- D5 CRC Error in Data Field: Controller detected a CRC error in the Data Field. Bit 5 of ST1 is also set.

- D4 Wrong Track: Only set if desired sector not found, and the track number recorded on any sector of the current track is different from that stored in the Track Register.

- D3 Scan Equal Hit: "Equal" condition satisfied during any Scan Command.

- D2 Scan Not Satisfied: Controller cannot find a sector on the track which meets the desired condition during Scan Command.

- D1 Bad Track: Only set if the desired sector is not found, and the track number recorded on any sector on the track is different from that stored in the Track Register and the recorded track number is FF.

- D0 Missing Address Mark in Data Field: Controller cannot find the Data Field Address Mark during Read/Scan command. Bit 0 of ST1 is also set.

# STATUS REGISTER 3 (ST3)

- D7 Not Used: 0

- **D6 Write Protect Status**

- D5 Not Used: 1

- D4 Track 0 Status

- D3 Not Used: 0

# D2 Head Select Status

- D1, D0 Drive Selected:

- 00 = Drive 0 selected. 01 = Drive 1 selected.

- 10 = Drive 2 selected. 11 = Drive 3 selected.

| TABLE VIII. Summary of FDC Registers |                          |                            |                             |                           |                      |                          |                    |                                           |  |  |

|--------------------------------------|--------------------------|----------------------------|-----------------------------|---------------------------|----------------------|--------------------------|--------------------|-------------------------------------------|--|--|

| Bits<br>Register                     | 7                        | 6                          | 5                           | 4                         | 3                    | 2                        | 1                  | 0                                         |  |  |

| DCR (W)                              | MTR3<br>Enable           | MTR2<br>Enable             | MTR1<br>Enable              | MTR0<br>Enable            | DMA<br>Enable        | Software<br>Reset        | Drive<br>Select 1  | Drive<br>Select 0                         |  |  |

| MSR (R)                              | Request<br>for<br>Master | Data<br>Direction          | Non-DMA<br>Execution        | Command<br>in<br>Progress | Drive 3<br>Seeking   | Drive 2<br>Seeking       | Drive 1<br>Seeking | Drive 0<br>Seeking                        |  |  |

| DR (R/W)                             | Data 7                   | Data 6                     | Data 5                      | Data 4                    | Data 3               | Data 2                   | Data 1             | Data 0                                    |  |  |

| DRR (W)                              | х                        | x                          | х                           | х                         | x                    | х                        | Data Rate<br>Bit 1 | Data Rate<br>Bit 0                        |  |  |

| DKR (R)                              | DSKCHG<br>Pin<br>Inverse | z                          | z                           | z                         | Z                    | z                        | z                  | z                                         |  |  |

| ST0                                  | Interrupt<br>Code        | Interrupt<br>Code          | Seek<br>End                 | No<br>Track 0             | 0                    | Head<br>Addr             | DRV 1<br>(Exec.)   | DRV 0<br>(Exec.)                          |  |  |

| ST1                                  | End<br>of<br>Track       | 0                          | CRC<br>Error                | Data<br>Overrun           | 0                    | No<br>Data               | WRT<br>PRT         | Missing<br>Address<br>Mark                |  |  |

| ST2                                  | 0                        | Control<br>Mark            | CRC<br>Error in<br>Data Fld | Wrong<br>Track            | Scan<br>Equal<br>Hit | Scan<br>Not<br>Satisfied | Bad<br>Track       | Missing<br>Address<br>Mark in<br>Data Fld |  |  |

| ST3                                  | 0                        | Write<br>Protect<br>Status | 1                           | Track 0<br>Status         | 0                    | Head<br>Select<br>Status | DRV 1<br>(Exec.)   | DRV 0<br>(Exec.)                          |  |  |

X = Don't CareZ = TRI-STATE

# **Processor Software Interface**

Bytes are transferred to and from the disk controller in different ways for the different phases in a command.

### COMMAND SEQUENCE

The disk controller can perform various disk transfer, and head movement commands. Most commands involve three separate phases.

**Command Phase:** The  $\mu$ P writes a series of bytes to the Data Register. These bytes indicate the command desired and the particular parameters required for the command. All the bytes must be written in the order specified in the Command Description Table. The Execution Phase starts immediately after the last byte in the Command Phase, the Drive Control and Data Rate Registers should be set.

**Execution Phase:** The disk controller performs the desired command. Some commands require the  $\mu$ P to read or write data to or from the Data Register during this time. Reading data from a disk is an example of this.

Result Phase: The  $\mu$ P reads a series of bytes from the data register. These bytes indicate whether the command exe-

cuted properly and other pertinent information. The bytes are read in the order specified in the Command Description Table.

A new command may be initiated by writing the Command Phase bytes after the last bytes required from the Result Phase have been read. If the next command requires selecting a different drive or changing the data rate the Drive Control and Data Rate Registers should be updated. If the command is the last command, then the software should deselect the drive. (*Note as a general rule the operation of the controller core is independent of how the*  $\mu$ *P updates the Drive Control and Data Rate Registers. The software must ensure that manipulation of these registers is coordinated with the controller operation.*)

During the Command Phase and the Result Phase, bytes are transferred to and from the Data Register. The Main Status Register is monitored by the software to determine when a data transfer can take place. Bit 6 of the Main Status Register must be clear and bit 7 must be set before a byte can be written to the Data Register during the Command Phase. Bits 6 and 7 of the Main Status Register must

# Processor Software Interface (Continued)

both be set before a byte can be read from the Data Register during the Result Phase.

If there is information to be transferred during the Execution Phase, there are three methods that can be used. The DMA mode is used if the system has a DMA controller. This allows the  $\mu$ P to do other things during the Execution Phase data transfer. If DMA is not used, an interrupt can be issued for each byte transferred during the Execution Phase. If interrupts are not used, the Main Status Register can be polled to indicate when a byte transfer is required.

# DMA MODE

If the DMA mode is selected, a DMA request will be generated in the Execution Phase when each byte is ready to be transferred. To enable DMA operations during the Execution Phase, the DMA mode bit in the Specify Command must be enabled, and the DMA signals must be enabled in the Drive Control Register. The DMA controller should respond to the DMA request with a DMA acknowledge and a read or write strobe. The DMA request will be cleared by the active edge of the DMA acknowledge. After the last byte is transferred, an interrupt is generated, indicating the beginning of the Result Phase. During DMA operations the Chip Select input must be held high. TC is asserted to terminate an operation. Due to the internal gating TC is only recognized when the DAK input is low.

# INTERRUPT MODE

If the non-DMA mode is selected, an interrupt will be generated in the Execution Phase when each byte is ready to be transferred. The Main Status Register should be read to verify that the interrupt is for a data transfer. Bits 5 and 7 of the Main Status Register will be set. The interrupt will be cleared when the byte is transferred to or from the Data Register. The  $\mu P$  should transfer the byte within the time allotted by Table VII. If the byte is not transferred within the time allotted, an Overrun Error will be indicated in the Result Phase when the command terminates at the end of the current sector.

An interrupt will also be generated after the last byte is transferred. This indicates the beginning of the Result Phase. Bits 7 and 6 of the Main Status Register will be set and bit 5 will be clear. This interrupt will be cleared by reading the first byte in the Result Phase.

#### SOFTWARE POLLING

If the non-DMA mode is selected and interrupts are not suitable, the  $\mu P$  can poll the Main Status Register during the Execution Phase to determine when a byte is ready to be transferred. In the non-DMA mode, bit 7 of the Main Status Register reflects the state of the interrupt pin. Otherwise, the data transfer is similar to the Interrupt Mode described above.

# **Command Description Table**

# READ DATA

# Command Phase

| MT            | MFM               | SK | 0 | 0 | 1  | 1   | 0   |  |  |  |  |

|---------------|-------------------|----|---|---|----|-----|-----|--|--|--|--|

| IPS           | х                 | х  | х | х | HD | DR1 | DR0 |  |  |  |  |

|               | Track Number      |    |   |   |    |     |     |  |  |  |  |

|               | Drive Head Number |    |   |   |    |     |     |  |  |  |  |

| Sector Number |                   |    |   |   |    |     |     |  |  |  |  |

|               |                   |    |   |   |    |     |     |  |  |  |  |

Number of Bytes per Sector

End of Track Sector Number

Intersector Gap Length

Data Length

Note 1

#### Result Phase

| Result Phas | se                |

|-------------|-------------------|

|             | Status Register 0 |

|             | Status Register 1 |

|             | Status Register 2 |

|             | Track Number      |

|             | Head Number       |

|             | Sector Number     |

|             | Bytes/Sector      |

# READ ID

Command Phase 0 MFM 0 0 1 0 1 0 X x x Х Х HD DR1 DR0 Result Phase Status Register 0 Status Register 1 Status Register 2 Track Number Head Number Sector Number

Bytes/Sector

####

| Command Phase               |                            |   |   |   |    |     |     |  |  |

|-----------------------------|----------------------------|---|---|---|----|-----|-----|--|--|

| 0                           | MFM                        | 0 | 0 | 1 | 1  | 0   | 1   |  |  |

| Х                           | х                          | Х | Х | Х | HD | DR1 | DR0 |  |  |

|                             | Number of Bytes per Sector |   |   |   |    |     |     |  |  |

| Number of Sectors per Track |                            |   |   |   |    |     |     |  |  |

|                             | Format Gap                 |   |   |   |    |     |     |  |  |

| Data Pattern                |                            |   |   |   |    |     |     |  |  |

|                             | Descult Diseas             |   |   |   |    |     |     |  |  |

#### **Result Phase**

| 165uit 1 lic | lesuit i nase     |  |  |  |  |  |  |

|--------------|-------------------|--|--|--|--|--|--|

|              | Status Register 0 |  |  |  |  |  |  |

|              | Status Register 1 |  |  |  |  |  |  |

|              | Status Register 2 |  |  |  |  |  |  |

|              | Track Number      |  |  |  |  |  |  |

|              | Head Number       |  |  |  |  |  |  |

|              | Sector Number     |  |  |  |  |  |  |

|              | Bytes/Sector      |  |  |  |  |  |  |

# Command Description Table (Continued)

# READ DELETED DATA

| Command Phase     |                   |        |        |        |        |     |     |

|-------------------|-------------------|--------|--------|--------|--------|-----|-----|

| MT                | MFM               | SK     | 0      | 1      | 1      | 0   | 0   |

| IPS               | Х                 | Х      | Х      | Х      | HD     | DR1 | DR0 |

|                   |                   | Т      | rack N | lumbe  | ər     |     |     |

|                   |                   | Driv   | e Hea  | d Nur  | nber   |     |     |

|                   |                   | S      | ector  | Numb   | er     |     |     |

|                   | Nu                | ımber  | of By  | tes pe | er Sec | tor |     |

|                   | En                | d of T | rack S | Sector | Num    | ber |     |

|                   |                   | Inters | ector  | Gap L  | .ength | ı   |     |

|                   |                   | I      | Data I | _ength | ı      |     |     |

| Resi              | ult Ph            | ase    |        |        |        |     |     |

|                   | Status Register 0 |        |        |        |        |     |     |

| Status Register 1 |                   |        |        |        |        |     |     |

| Status Register 2 |                   |        |        |        |        |     |     |

| Track Number      |                   |        |        |        |        |     |     |

Head Number Sector Number Bytes/Sector

# WRITE DATA

| Command Phase          |     |                 |         |        |        |     |     |  |

|------------------------|-----|-----------------|---------|--------|--------|-----|-----|--|

| MT                     | MFM | MFM 0 0 0 1 0 1 |         |        |        |     |     |  |

| IPS                    | Х   | х               | х       | Х      | HD     | DR1 | DR0 |  |

|                        |     | Т               | rack N  | lumbe  | ər     |     |     |  |

|                        |     | Driv            | e Hea   | d Nur  | nber   |     |     |  |

|                        |     | S               | ector I | Numb   | er     |     |     |  |

|                        | Nu  | ımber           | of By   | tes pe | er Sec | tor |     |  |

|                        | En  | d of T          | rack S  | Sector | Num    | ber |     |  |

| Intersector Gap Length |     |                 |         |        |        |     |     |  |

| Data Length            |     |                 |         |        |        |     |     |  |

| Dool                   |     |                 |         |        |        |     |     |  |

| Result Phase      |  |

|-------------------|--|

| Status Register 0 |  |

| Status Register 1 |  |

| Status Register 2 |  |

| Track Number      |  |

| Head Number       |  |

| Sector Number     |  |

| Bytes/Sector      |  |

# SCAN EQUAL

| Command Phase              |                   |       |       |           |        |     |     |  |  |

|----------------------------|-------------------|-------|-------|-----------|--------|-----|-----|--|--|

| ΜТ                         | MFM               | SK    | 1     | 1 0 0 0 1 |        |     |     |  |  |

| IPS                        | х                 | Х     | Х     | Х         | HD     | DR1 | DR0 |  |  |

|                            | Track Number      |       |       |           |        |     |     |  |  |

|                            | Drive Head Number |       |       |           |        |     |     |  |  |

| Sector Number              |                   |       |       |           |        |     |     |  |  |

|                            | Nu                | Imber | of By | tes pe    | er Sec | tor |     |  |  |

| End of Track Sector Number |                   |       |       |           |        |     |     |  |  |

| Intersector Gap Length     |                   |       |       |           |        |     |     |  |  |

| Sector Step Size           |                   |       |       |           |        |     |     |  |  |

# Result Phase

| Ticouit i Tidoc   |  |

|-------------------|--|

| Status Register 0 |  |

| Status Register 1 |  |

| Status Register 2 |  |

| Track Number      |  |

| Head Number       |  |

| Sector Number     |  |

| Bytes/Sector      |  |

# **READ A TRACK**

| Command Phase     |        |        |        |        |        |     |     |

|-------------------|--------|--------|--------|--------|--------|-----|-----|

| 0                 | MFM    | SK     | 0      | 0      | 0      | 1   | 0   |

| IPS               | х      | Х      | х      | х      | HD     | DR1 | DR0 |

|                   |        | Т      | rack N | lumbe  | ər     |     |     |

|                   |        | Driv   | e Hea  | d Nur  | nber   |     |     |

|                   |        | S      | ector  | Numb   | er     |     |     |

|                   | Nu     | mber   | of By  | tes pe | er Sec | tor |     |

|                   | En     | d of T | rack S | Sector | Num    | ber |     |

|                   | I      | Inters | ector  | Gap L  | .ength | 1   |     |

|                   |        | I      | Data I | ength  | ı      |     |     |

| Resi              | ult Ph | ase    |        |        |        |     |     |

|                   |        | Sta    | atus R | egiste | er O   |     |     |

|                   |        | Sta    | atus R | egiste | er 1   |     |     |

| Status Register 2 |        |        |        |        |        |     |     |

| Track Number      |        |        |        |        |        |     |     |

| Head Number       |        |        |        |        |        |     |     |

|                   |        | S      | ector  | Numb   | er     |     |     |

Bytes/Sector

# WRITE DELETED DATA

| Command Phase |                        |        |           |        |        |     |     |  |  |

|---------------|------------------------|--------|-----------|--------|--------|-----|-----|--|--|

| MT            | MFM                    | 0      | 0 1 0 0 1 |        |        |     |     |  |  |

| IPS           | х                      | Х      | Х         | Х      | HD     | DR1 | DR0 |  |  |

|               | Track Number           |        |           |        |        |     |     |  |  |

|               |                        | Driv   | e Hea     | d Nur  | nber   |     |     |  |  |

|               |                        | S      | ector I   | Numb   | er     |     |     |  |  |

|               | Nu                     | ımber  | of By     | tes pe | er Sec | tor |     |  |  |

|               | En                     | d of T | rack S    | Sector | Num    | ber |     |  |  |

|               | Intersector Gap Length |        |           |        |        |     |     |  |  |

|               | Data Length            |        |           |        |        |     |     |  |  |

|               |                        |        |           |        |        |     |     |  |  |

# Result Phase

| Sult i lic | 130               |

|------------|-------------------|

|            | Status Register 0 |